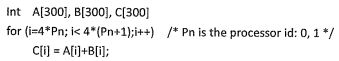

題組內容

6.(20 pts) Consider a SMP processor (Symmetric Multiprocessor) adopting the Write-Invalidate Snooping Cache

Cohorence protocol. Each processor has a 4KiB direct-mapped, physically-addressed L1 cache with 16-byte cache lines. Three

integer arrays A, B and C are placed contiguously in the memory in the order of A, B and C. The starting address of array A is

0x0000A000 (assuming 32-bit memory address). Processor Po and P1 execute the following code segment (the L1 cache is

empty initially):