題組內容

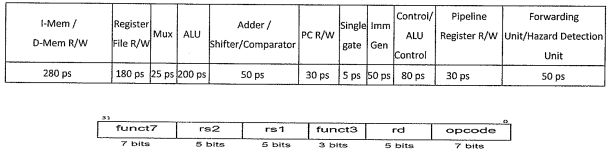

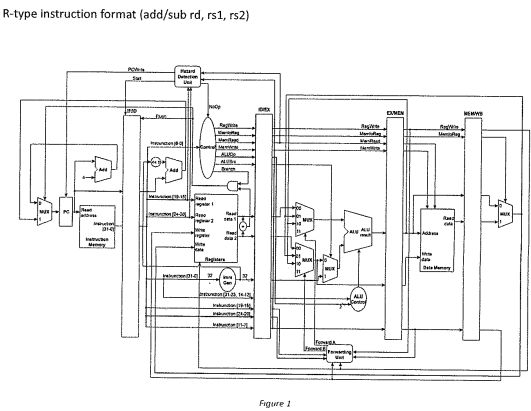

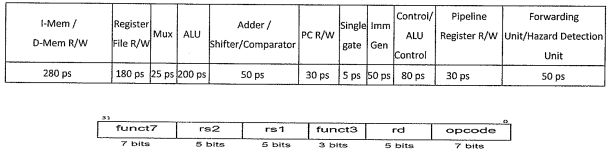

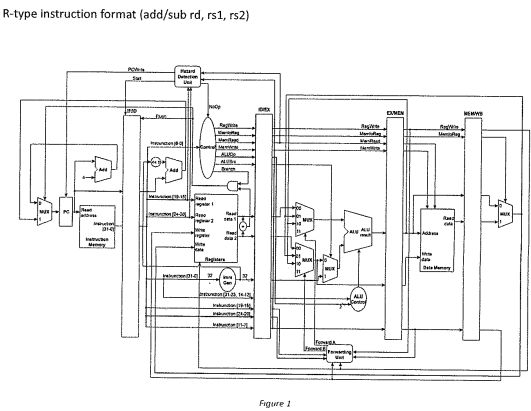

7.(25 pts) Consider a 5-stage (IF, ID, EX, MEM, WB) RISC-V pipelined processor (Figure 1) composed of logic blocks with the

following latency (any unspecified block latency is treated as O):

7.(25 pts) Consider a 5-stage (IF, ID, EX, MEM, WB) RISC-V pipelined processor (Figure 1) composed of logic blocks with the

following latency (any unspecified block latency is treated as O):